您好,歡迎光臨帝國科技!

帝國博客

更多>>LVPECL和LVDS差分輸出低噪音晶體振蕩器電路圖

來源:http://www.mlnic.org.cn 作者:帝國科技工程部 2016年06月21

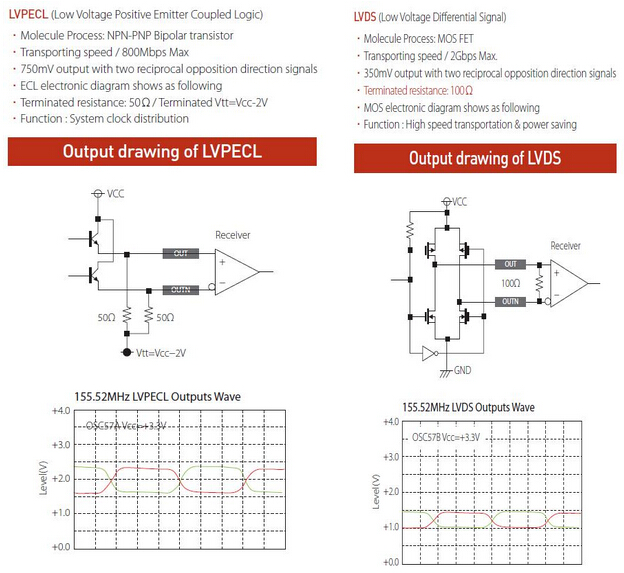

在過去,電腦一直在快速移動的總線接口驅動電壓5V的TTL和CMOS驅動電壓3.3V LVTTL和LVCMOS主流.最近人們大多是需要高速總線接口和開發成功的千兆以太網技術,可以傳輸Gbps.然而,在g傳輸時鐘將超過100 mhz更高時,噪音的影響將會非常明顯.因此需要高質量的石英晶體振蕩器,臺灣希華研發出OSC57A,OSC57B和SEV-7050幾款.它們都是差分LVPECL和LVDS接口輸出.此外,這些可以用于高速傳輸,并且可以降低噪聲的影響.

下面的圖表顯示LVPECL和LVDS輸出電路

下面的圖表顯示LVPECL和LVDS輸出電路

正在載入評論數據...

相關資訊

- [2026-02-05]CRYSTEK打破時鐘精度天花板CCSO-914X超低相位噪聲晶振來襲

- [2026-01-27]信號抖動終結者Suntsu松圖超低抖動振蕩器來襲

- [2026-01-22]TAITIEN時鐘憑借計時功能和GPS同步技術成為不可或缺的時間保障

- [2026-01-22]TAITIEN泰藝晶振的低功耗OCXO技術開啟電子新時代

- [2024-03-18]Raltron產品和技術應用說明CO13050-32.000-T-TR

- [2024-03-13]Bliley恒溫晶振BOVTE-50MDA-DCCB的保質期有多長?

- [2024-03-05]Renesas推出RA8T1系列低功耗MCU

- [2024-03-04]Vishay推出VEMD2704具有提高了可見光靈敏度

業務經理

業務經理